# PCA-1248

8x 12-bit. ADC 2MB RAM, DAC IRQ, 8+8 DIO

## Důležité upozornění!

Při zacházení s kartou dbejte zásad mani pulace s obvody citlivými na poškození elektrostatickým nábojem.

Instalaci provádějte zásadně při vypnutém počítači a vždy odpojte síťový kabel a přívodní vodiče karty!

Při nedodržení uvedených pravi del může dojít k trvalému poškození citlivých obvodů PC karty nebo celého počítače.

Uži vatelská příručka a její součásti jsou autorským dílem chráněným ustanovením zákona č. 35/1965 Sb. o dílech li terárních, vědeckých a uměleckých (Autorský zákon) ve znění zákona č. 89/1990 Sb., zákona č. 468/1991 Sb., zákona č. 318/1993 Sb., zákona č. 237/1995 Sb. a zákona č. 86/1996 Sb.

Všechna jména a názvy použi té v textu mohou být chráněnými známkami nebo obchodními názvy výrobků příslušných firem.

© 1994÷2000 TEDIA spol. s r. o.

Záruční a pozáruční servis:

TEDIA spol. s r. o., Zábělská 12, 312 11 Plzeň 12

telefon: 019 7478168 fax: 019 7478169 e-mail: tedia@tedia.cz internet: http://www.tedia.cz

## Obsah

| 1.           | Úvodní popis                                    | Ī 1            |

|--------------|-------------------------------------------------|----------------|

| 1.1.         | Charakteristika                                 | I - 1          |

| 2.           | Technické parametry                             |                |

| 2.1.         | A/D převodník                                   | I - 2          |

| 2.2.         | Logika spouštění                                | I - 2          |

| 2.3.<br>2.4. | D/A převodník<br>Obvody analogové synchronizace | I - 2<br>I - 2 |

| 2.5.         | Multicard master slave logika                   | I - 2<br>I - 3 |

| 2.6.         | Obvody přerušení                                | I - 3          |

| 2.7.         | Digitální porty                                 | I - 3          |

| 2.8.         | Ostatní údaje                                   | I - 3          |

| 2.9.         | Modul XM-1248                                   | I - 3          |

| 3.           | Instalace karty                                 |                |

| 3.1.         | Úvod                                            | I - 4          |

| 3.2.         | Nastavení bázové adresy                         | I - 4          |

| 3.3.         | Vlastní instalace                               | I - 4          |

| 3.4.         | Zapojení konektorů                              | I - 4          |

| 3.5.         | Rozmístění přepínačů, trimrů a konektorů        | I - 4          |

| 4.           | Struktura adresového prostoru karty             |                |

| 4.1.         | Popis adresového dekodéru                       | I - 5          |

| 4.2.         | ScanReg                                         | I - 5          |

| 4.3.         | CWReg                                           | I - 5          |

| 4.4.         | StatusReg                                       | I - 6          |

| 4.5.<br>4.6. | ADCTrigReg<br>RAMDataReg                        | I - 7<br>I - 7 |

| 4.7.         | RAMAdrReg                                       | I - 8          |

| 4.8.         | IRQReg                                          | I - 8          |

| 4.9.         | SyncReg                                         | I - 9          |

| 4.10.        | •                                               | I - 9          |

| 4.11.        | DigOutReg                                       | I - 10         |

| 4.12.        | DigInReg                                        | I - 10         |

| 5.           | Popis scanovací logiky                          |                |

| 5.1.         | Úvod                                            | I - 11         |

| 5.2.         | Programování                                    | I - 11         |

| 5.3.         | Činnost v průběhu měření                        | I - 11         |

| 5.4.         | Příklad programové obsluhy                      | I - 11         |

| 6.           | Popis taktovacích generátorů                    |                |

| 6.1.         | Úvod                                            | I - 12         |

| 6.2.         | Zapojení taktovacích generátorů                 | I - 12         |

| 6.3.         | Programování taktovacích generátorů             | I - 12         |

| 7.    | Popis řadiče přerušení             |        |

|-------|------------------------------------|--------|

| 8.1.  | Úvod                               | I - 13 |

| 8.2.  | Zdroje přerušení                   | I - 13 |

| 8.    | Popis obvodů lokální sběrnice      |        |

| 8.1.  | Úvod                               | I - 14 |

| 8.2.  | Externí signály                    | I - 14 |

| 8.3.  | Řídicí signály                     | I - 14 |

| 9.    | Popis digitálních vstupů a výstupů |        |

| 9.1.  | Úvod                               | I - 15 |

| 9.2.  | Zapojení vstupů                    | I - 15 |

| 9.3.  | Zapojení výstupů                   | I - 15 |

| 10.   | Popis programové obsluhy           |        |

| 10.1. | Úvod                               | I - 16 |

| 10.2. | Struktura paměti RAM               | I - 16 |

| 10.3. | Režim spouštění časovačem          | I - 16 |

| 10.4. | Režim spouštění externím signálem  | I - 17 |

| 10.5. | Režim programového spouštění       | I - 17 |

| 10.6. | Přenos dat do operační paměti      | I - 17 |

Přílohy: Příloha II - tabulky Příloha III - obrázky

## 1. Úvodní popis

#### 1.1. Charakteristika

Měřicí PC karta PCA-1248 je výrobek moderní koncepce ze stavebnice karet CHALLENGE SERIE určené zejména pro laboratorní a průmyslová měření s vyššími nároky na vzorkovací frekvenci apod.

Karta PCA-1248 byla realizována na bázi moderních A/D a D/A převodníků firmy Analog Devices a vzhledem k nestandardnímu obvodovému řešení dosahuje příznivých parametrů. Aplikační možnosti rozšiřují digitální vstupy a výstupy. K přednostem karty patří jednoduchá programová konfigurovatelnost parametrů. Při vlastní instalaci karty do počítače je nutné hardwarově nastavit pouze bázovou adresu; všechny ostatní funkce karty jsou ovládány plně softwarově.

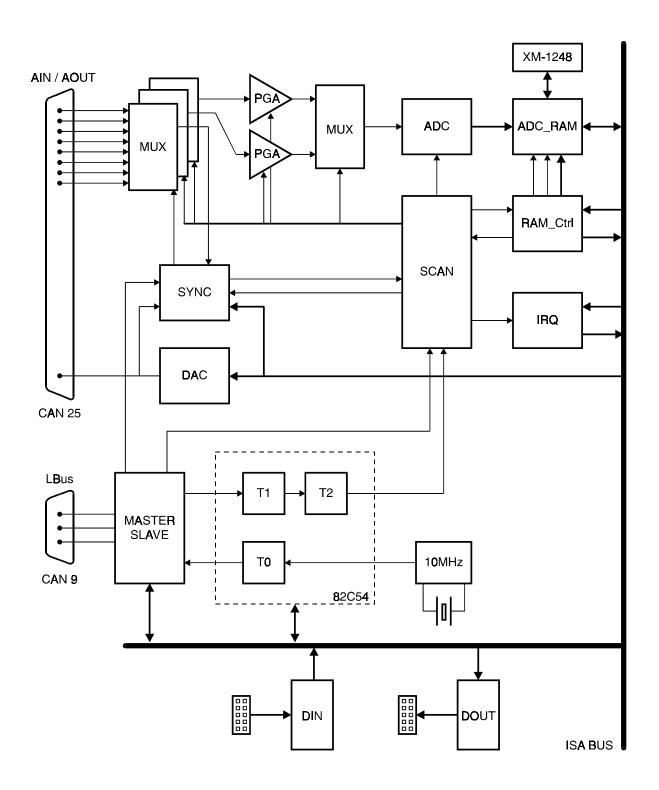

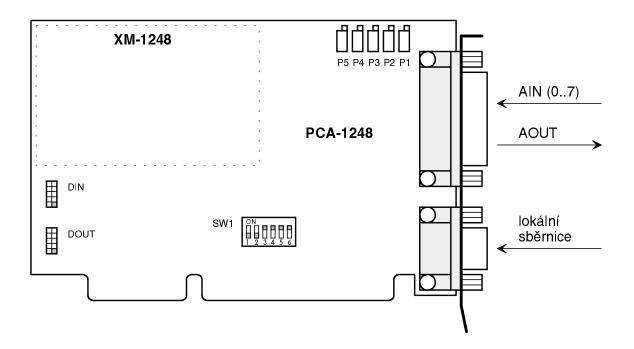

Celkový pohled na desku PCA-1248 a její vnitřní obvodová struktura jsou zakresleny na obrázcích Obr.1. a Obr.2.

Karta PCA-1248 se vyznačuje zejména těmito vlastnostmi:

- 12-bitový A/D převodník

- multiplexer pro 8 S.E. vstupů

- zesilovač s programovatelným ziskem

- časovač pro periodické spouštění převodníku

- záznamové obvody s pamětí RAM 2MB (možnost rozšíření na 8MB)

- logika přerušení s kompletním programovým řízením (IRQ2÷IRQ11)

- 8+8 digitálních kanálů

- 16-bitový ISA interface

#### Mimořádné vlastnosti:

- dvoukanálové řešení vstupních obvodů

- "multicard master-slave" logika pro synchronizaci všech PC karet systému

Svojí koncepcí je určena zejména pro:

- standardní měření se vzorkovacím kmitočtem do 1MHz

- realizaci výkonných autonomních měřicích ústředen (s využití "multicard master-slave" logiky)

## 2. Technické parametry

## 2.1. A/D převodník

rozlišení: 12 bitů (AD7892)

počet vstupů: 8 S.E.

doba ustálení vstupního zesilovače: 1µs (viz pozn.)

vstupní impedance:  $10M\Omega$  typ.

vstupní rozsahy: ±5V

maximální vstupní napětí: ±24V (viz pozn.)

programovatelné zesílení: 1x, 5x

přesnost nastaveného zesílení:  $\pm 0.1\%$  typ.  $(\pm 0.5\%$  max.)

囱

Doba ustálení platí v případě, kdy vstupní napětí nepřekročí vstupní rozsah více než o 20%. Při překročení maximálního vstupního napětí může dojít k trvalému poškození obvodů karty.

### 2.2. Logika spouštění

zdroje spouštění A/D převodníku: programově, interní časovač,

externí signál TTL (sestupná hrana)

rozsah nastavení spouštění časovačem: do 6ms s rozlišením 100ns

doba A/D konverze: 1μs (viz pozn.)

maximální rychlost vzorkování: 1MHz

ovládané funkce scanovací logiky: fyzický vstup karty (IN0 ÷ IN7)

zesílení (1x, 5x)

vyrovnávací paměť: RAM 2MB (tzn. 1048576 vzorků)

RAM 8MB (s modulem XM-1248)

2

Vzhledem k dvoukanálovému řešení vstupních obvodů se vstupní zesilovač ustaluje v průběhu měření předcházejícího kanálu v sekvenci.

## 2.3. D/A převodník

rozlišení: 8 bitů počet výstupů: 1 výstupní rozsahy: ±5V

zatěžovací impedance: 500Ω min. (viz pozn.)

2

Výstup D/A převodníku je odolný proti trvalému zkratu proti GND.

Přivedením vnějšího napětí mimo rozsah ±12V dojde k nevratnému poškození obvodů.

### 2.4. Obvody analogové synchronizace

vstupy pro synchronizaci: 8x S.E. vstup (programová volba)

komparační úroveň: ±5V

aktivní úroveň analog. signálu: naběžná/sestupná hrana

🙇 Karta PCA-1248 umožňuje rovněž synchronizaci externím TTL signálem.

rev. 04.2000 I - 2

#### 2.5. Multicard master slave logika

podporované signály: taktovací generátor ADC

externí taktovací TTL signál

externí synchronizační TTL signál

10x PCA-1248 max. kapacita lokální sběrnice:

délka 25cm max.

#### Obvody přerušení 2.6.

zdroje přerušení: EOC ADC (konec měření) IRO kanál: IRO2 ÷ IRO11 (volen programově)

#### 2.7. Digitální porty

8 (TTL komp.) počet vstupů: 8 počet výstupů: (TTL komp.) zatěžovací impedance výstupů:  $500\Omega$  min. (viz pozn.)

2

Vstupní porty jsou odolné proti přepětí ±24V. Výstupní digitální porty jsou odolné proti trvalému zkratu proti GND; přivedením napětí mimo rozsah 0÷5V dojde k nevratnému poškození obvodů.

#### 2.8. Ostatní údaje

| I/O adresa:      | $200_{H} \div 3F0_{H}$ | (32 intervalů) |

|------------------|------------------------|----------------|

| •                | 11 11                  | ,              |

| napájecí napětí: | +5V                    | (500 mA max.)  |

|                  | +12V                   | (200 mA max.)  |

|                  | -12V                   | (50 mA max.)   |

| rozměry:         | cca 105 x 185 mm       |                |

| EMC:             | ČSN EN 55022           |                |

|                  | ČSN EN 50081-1         |                |

CSN EN 50081-1 ČSN EN 50082-1

#### Modul XM-1248 2.9.

Karta PCA-1248 je umožňuje rozšíření základní RAM násuvným modulem dodávaným pod označením XM-1248.

vyrovnávací paměť: 6MB (tzn. celkem 8MB) napájecí napětí: +5V(600 mA max.) rozměry: cca 50 x 100 mm

2

Modul XM-1248 rozšíří základní pamět karty na 8MB; přítomnost XM-1248 je detekována automaticky obvody karty a nevyžaduje proto žádné konfigurační zásahy.

## 3. Instalace karty

## 3.1. Úvod

Při výrobě bylo dbáno na dosažení vysoké kvality a spolehlivosti, rovněž byla věnována pozornost důkladné kontrole před expedicí. Aby nedošlo ke snížení jakosti či poškození při instalaci, doporučujeme Vám pečlivě prostudovat tuto příručku a postupovat podle uvedeného návodu.

## 3.2. Nastavení bázové adresy

Bázovou adresu PC karty lze nastavit v rozsahu 200<sub>H</sub> až 3F0<sub>H</sub>. Volba se provádí prostřednictvím šestinásobného DIL přepínače DIL SW1; význam jednotlivých segmentů je vyznačen v tabulce Tab.1. Při volbě je třeba dbát, aby nedošlo ke kolizi s ostatními instalovanými I/O zařízeními. Seznam standardních zařízení umístěných v tomto intervalu adres je uveden v tabulce Tab.2.

#### 3.3. Vlastní instalace

Instalaci karty provádějte zásadně při vypnutém počítači s odpojenými přívodními vodiči (síť, monitor apod.) a dodržujte zásady pro manipulaci s obvody citlivými na poškození elektrostatickým nábojem. S kartou manipulujte za okraje a nedotýkejte se prsty součástek. Nakonfigurovanou kartu zasuňte po předchozím vyjmutí krycího štítku do volné pozice pro rozšiřující desky počítače a zajistěte šroubem.

## 3.4. Zapojení konektorů

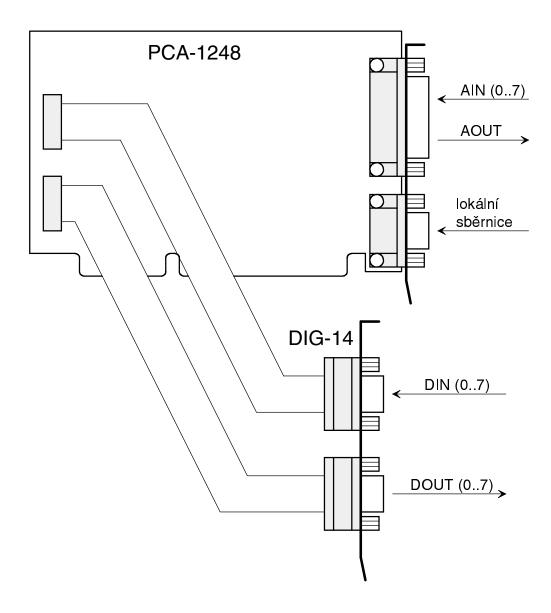

Zapojení vývodů konektorů je zakresleno na obrázcích Obr.3. až Obr.5.; popis signálů je uveden v tabulkách Tab.3. až Tab.5. V případě využití propojovacího kabelu DIG-14 pro zpřístupnění digitálních portů na zadním PC štítku (viz Obr.6.) je zapojení konektorů popsáno v tabulce Tab.6.

Připojení desky k měřenému objektu je naznačeno na obrázcích Obr.7. až Obr.10.

## 3.5. Rozmístění přepínačů, trimrů a konektorů

Rozmístění přepínačů, trimrů a konektorů na kartě PCA-1248 je zakresleno na obrázku Obr.2.; význam jednotlivých prvků je zřejmý z předešlých odstavců.

rev. 04,2000

## 4. Struktura adresového prostoru

### 4.1. Popis adresového dekodéru

Adresový dekodér umožňuje relokaci bázové adresy karty v rozsahu  $200_{\rm H}$  až  $3{\rm F}0_{\rm H}$ . Protože karta zabírá celkem 16 I/O adres, lze volit jeden z 32 intervalů.

Karta obsahuje několik typů registrů:

řídicí:

• jsou určeny pro řízení režimu desky

(DACModeReg, ADCModeReg, LBusReg, ...)

datové:

• jsou určeny pro přenos dat

(ADCReg, DACReg)

DIO:

• slouží k přímému řízení digitálních portů (vstupní i výstupní)

(DigInReg, DigOutReg)

Struktura registrů v adresovém prostoru je přehledně uvedena v tabulce Tab.7.

## 4.2. ScanReg

(WR, Base+A)

Registr ScanReg slouží k programování obsahu paměti scanovacích parametrů; registr přenáší současně číslo kanálu v sekvenci (tzn. adresu paměťové buňky) i scanovací parametr (tzn. data zapisovaná do paměti). V průběhu měření pak registr uchovává informaci o počtu měřených kanálů v sekvenci.

Struktura registru a význam jednotlivých bitů je následující:

| D7   | D6 | D5    | D4 | D3   | D2 | D1  | D0 |

|------|----|-------|----|------|----|-----|----|

| SLOW |    | CH_Nr |    | GAIN |    | MUX |    |

MUX • ovládání vstupního multiplexeru analogový vstup "Analog In 0" 000 analogový vstup "Analog In 1" 001 . . . analogový vstup "Analog In 7" 111 **GAIN** • ovládání zesílení vstupního zesilovače zesílení 1x (tzn. rozsah ±5V) zesílení 5x (tzn. rozsah ±1V) 1 CH\_Nr číslo kanálu ve scanovací sekvenci 000 kanál číslo "CH0" (první měřený kanál) 001 kanál číslo "CH1" . . . . . . . . . . . . . . . . . . kanál číslo "CH7" 111 • doba konverze A/D převodníku (společně pro všechny kanály) **SLOW** doba převodu 1µs 0 1 doba převodu 1,6µs

## 4.3. CWReg

(WR, Base+B)

Tento registr slouží k řízení všech základních funkcí a režimů karty. Struktura registru a význam jednotlivých bitů je následující:

| D7   | D6   | D5    | D4    | D3 | D2 | D1 | D0  |

|------|------|-------|-------|----|----|----|-----|

| LBEN | MODE | IncWR | IncRD | SY | NC | TR | RIG |

| TRIG         | • slouží k volb                               | ě zdroje spouštění měřicích sekvencí                                                                                                                                                                                     |

|--------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11110        |                                               | pepovolen žádný ze zdrojů periodického spouštění                                                                                                                                                                         |

|              |                                               | lze spouštět programovým pulsem)                                                                                                                                                                                         |

|              |                                               | pouštění interním časovačem                                                                                                                                                                                              |

|              | 10 s                                          | pouštění externími pulsy                                                                                                                                                                                                 |

|              | 11 r                                          | ezerva                                                                                                                                                                                                                   |

| SYNC         | <ul> <li>slouží k volb</li> </ul>             | ě zdroje synchronizační události                                                                                                                                                                                         |

|              | 00 s                                          | ynchronizační logika neaktivována                                                                                                                                                                                        |

|              | 01 -> 00 t                                    | rigovací puls vygenerován programově                                                                                                                                                                                     |

|              |                                               | xterní trigovací signál karty (Cannon 9)                                                                                                                                                                                 |

|              |                                               | TTL signál, sestupná hrana)                                                                                                                                                                                              |

|              |                                               | ignál z analogového vstupu                                                                                                                                                                                               |

|              | (                                             | parametry viz další popis registrů)                                                                                                                                                                                      |

| IncRD        |                                               | e adresových registrů RAM při čtení dat                                                                                                                                                                                  |

|              |                                               | nkrementace nepovolena                                                                                                                                                                                                   |

|              |                                               | nkrementace povolena                                                                                                                                                                                                     |

| IncWR        |                                               | e adresových registrů RAM při zápisu dat                                                                                                                                                                                 |

|              |                                               | nkrementace nepovolena                                                                                                                                                                                                   |

|              | 1 i:                                          | nkrementace povolena                                                                                                                                                                                                     |

|              |                                               | 1                                                                                                                                                                                                                        |

| MODE         |                                               | idní režimy desky, resp. přístup do RAM, a je                                                                                                                                                                            |

| MODE         | současně vyt                                  | idní režimy desky, resp. přístup do RAM, a je<br>ižit pro nulování vybraných stavových příznaků                                                                                                                          |

| MODE         | současně vyu<br>0 H                           | ndní režimy desky, resp. přístup do RAM, a je<br>nžit pro nulování vybraných stavových příznaků<br>RAM přidělena sběrnici ISA, karta neměří                                                                              |

|              | současně vyt<br>0 F<br>1 F                    | dní režimy desky, resp. přístup do RAM, a je<br>ižit pro nulování vybraných stavových příznaků<br>RAM přidělena sběrnici ISA, karta neměří<br>RAM přidělena scanovací logice a A/D převodníku                            |

| MODE<br>LBEN | současně vyt<br>0 F<br>1 F<br>• slouží k volb | idní režimy desky, resp. přístup do RAM, a je ižit pro nulování vybraných stavových příznaků RAM přidělena sběrnici ISA, karta neměří RAM přidělena scanovací logice a A/D převodníku ě režimu lokální sběrnice PC karty |

|              | současně vyu 0 F 1 F • slouží k volb 0 b      | dní režimy desky, resp. přístup do RAM, a je<br>ižit pro nulování vybraných stavových příznaků<br>RAM přidělena sběrnici ISA, karta neměří<br>RAM přidělena scanovací logice a A/D převodníku                            |

## 4.4. StatusReg

(RD, Base+B)

Tento registr signalizuje aktuální stav probíhajícího měření a současně je vyhrazen pro další stavové příznaky.

Struktura registru a význam jednotlivých bitů je následující:

| D7  | D6 | D5 | D4  | D3   | D2 | D1  | D0  |

|-----|----|----|-----|------|----|-----|-----|

| CMP | RS | RV | EOC | RSRV |    | AD_ | STS |

AD\_STS

• slouží k volbě zdroje spouštění měřicích sekvencí

00 měření neprobíhá

01 měření před detekcí synchronizační události

10 rezerva

11 měření po detekci synchronizační události

EOC

• příznak signalizující ukončení měření, popř. vyvolání přerušení (aktivní v úrovni H, nulován pomocí CWReg - MODE=0)

**CMP**

výstup napěťového komparátoru synchronizačních obvodů

0 zvolený signál má menší napětí než komparační práh

1 zvolený signál má větší napětí než komparační práh

**RSRV**

rezerva

2

Komparační práh je nastaven pomocí D/A převodníku, dále viz popis DACReg a SyncReg.

### 4.5. ADCTrigReg

(WR, Base+9)

Tento registr slouží k povolení spouštění měřicí sekvence časovačem PC karty, resp. extením TTL signálem; současně je využit i k programovému spouštění. Struktura registru a význam jednotlivých bitů je následující:

| D7    | D6     | D5 | D4 | D3 | D2 | D1 | D0 |

|-------|--------|----|----|----|----|----|----|

| SW_St | TIM_St |    |    | RS | RV |    |    |

TIM St

• slouží k zahájení měření časovačem nebo externím signálem (úrovní H je povoleno generování startovacích pulsů, registr je nulován pomocí CWReg - MODE=0)

SW\_St

slouží k programovému spuštění jedné měřicí sekvence (zápisem úrovně H je vygenerován jeden startovací puls)

**RSRV**

• rezerva

Rezervní bity nemají pro funkci desky žádný význam, z důvodu dopředné kompatibility je však doporučena logická úroveň L.

### 4.6. RAMDataReg

(WR/RD, Base+8)

Registr RAMDataReg slouží k přenosu dat A/D převodníku uložených v průběhu měření do datové paměti RAM.

Operace čtení/zápis registru RAMDataReg mohou být využity pro automatickou inkrementaci adresy RAM (viz popis CWReg).

Registr je přístupný výhradně prostřednictvím 16-bitového I/O cyklu sběrnice. Struktura dat a význam jednotlivých bitů je následující:

| D15  | D14 | D13 | D12 | D11 D0       |

|------|-----|-----|-----|--------------|

| FRST | TRG | L   | L   | ADC (D11 D0) |

**ADC**

data A/D převodníku v přímém binárním kódu

-5.0000V výstupní kód 0000 0000 0000 -0.0024V výstupní kód 0111 1111 1111 0.0000V výstupní kód 1000 0000 0000 0.0024V výstupní kód 1000 0000 0001 4.9976V výstupní kód 1111 1111 1111

$\mathbf{e}$

#### Důležité upozornění.

Příznak TRG je korektně nastavován pouze u karty master. Příznak FRST je aktivní pouze při měření 2 a více kanálů.

## 4.7. RAMAdrReg

#### (WR/RD, Base+C/D/E)

Registr RAMAdrReg je složen ze tří 8-bitových registrů umístěných na navazujících I/O adresách; nejnižší adresové bity jsou uloženy na adrese Base+C, nejvyšší pak na adrese Base+E.

Z plného rozsahu 24 bitů karta PCA-1248 využívá pouze 20 nižších bitů; v případě rozšíření násuvným modulem XM-1248 je využito 22 bitů. Nevyužité bity jsou při zápisu nevýznamné, při čtení jsou trvale v úrovni L.

Kromě možnosti přímého zápisu adresy RAM karta umožňuje automatickou inkrementaci adresy při čtení, resp. zápisu do paměti a tím zásadně zefektivnit přenos naměřených dat do operační paměti počítače (viz popis CWReg).

Přítomnost XM-1248 a přepnutí adresového rozsahu je provedeno automaticky obvody karty.

## 4.8. IRQReg

(WR, Base+7)

Tento registr slouží k povolení funkce přerušení a volbě kanálu IRQ. Registr je po resetu, resp. zapnutí počítače vynulován.

Struktura registru a význam jednotlivých bitů je následující:

| D7 | D6 | D5 | D4 | D3 | D2 | D1    | D0 |

|----|----|----|----|----|----|-------|----|

|    | RS | RV |    |    | IR | . ( ) |    |

IRQ • definují IRQ kanál ISA sběrnice

0000 není přiřazen žádný kanál IRQ

0010 přiřazen kanál IRQ2/IRQ9

0011 přiřazen kanál IRQ3

....

0111 přiřazen kanál IRQ7

1010 přiřazen kanál IRQ10

1011 přiřazen kanál IRQ11

**RSRV**

• rezerva

2

Rezervní bity nemají pro funkci desky žádný význam, z důvodu dopředné kompatibility je však doporučena logická úroveň L. Neuvedené kombinace D3÷D0 jsou rezervovány.

### 4.9. SyncReg

(WR, Base+5)

Tento registr slouží k volbě analogového signálu určeného pro synchronizaci (viz popis CWReg). Registr je po resetu, resp. zapnutí počítače vynulován. Struktura registru a význam jednotlivých bitů je následující:

| D7 | D6   | D5 | D4  | D3   | D2 | D1 | D0 |

|----|------|----|-----|------|----|----|----|

|    | RSRV |    | SLP | RSRV |    |    |    |

SyncMUX

• ovládání vstupního multiplexeru synchronizačních obvodů

analogový vstup "Analog In 0"

analogový vstup "Analog In 1"

analogový vstup "Analog In 7"

**SLP**

• volba náběžné nebo sestupné hrany signálu

synchronizace překročením hladiny definované DAC

synchronizace poklesem pod hladinu definovanou DAC

RSRV • rezerva

### 4.10. DACReg

(WR, Base+4)

Tento registr slouží k programování D/A převodníku využitého současně jako pomocný analogový výstup a pro komparační hladinu synchronizačních obvodů. Obsah registru není po resetu, resp. zapnutí počítače definován. Struktura registru a význam jednotlivých bitů je následující:

| D7 | D6 | D5 | D4       | D3     | D2 | D1 | D0 |

|----|----|----|----------|--------|----|----|----|

|    |    |    | DAC_0 (I | D7 D0) |    |    |    |

$DAC_0$

- data D/A převodníku v přímém binárním kódu

- napětí na výstupu Analog Out 0 a komparační hladina synchronizačních obvodů

-5.00V vstupní kód 0000 0000 vstupní kód 0000 0001 ... 0.00V vstupní kód 1000 0000 vstupní kód 1000 0000 vstupní kód 1000 0001 ... 4.96V vstupní kód 1111 1111

rev. 04.2000 I - 9

## 4.11. DigOutReg

(WR, Base+F)

Tento registr plní funkci výstupního digitálního portu; význam jednotlivých bitů je zřejmý ze struktury registru a zapojení konektoru portu.

Registr je po resetu, resp. zapnutí počítače vynulován.

| D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

|-------|-------|-------|-------|-------|-------|-------|-------|

| DOUT7 | DOUT6 | DOUT5 | DOUT4 | DOUT3 | DOUT2 | DOUT1 | DOUT0 |

## 4.12. DigInReg

(RD, Base+F)

Tento registr plní funkci vstupního digitálního portu; význam jednotlivých bitů je zřejmý ze struktury registru a zapojení konektoru portu.

| D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0   |

|------|------|------|------|------|------|------|------|

| DIN7 | DIN6 | DIN5 | DIN4 | DIN3 | DIN2 | DIN1 | DIN0 |

rev. 04.2000 I - 10

## 5. Popis scanovací logiky

## 5.1. Úvod

Karta PCA-1248 je vybavena scanovací logikou pro automatické odměření požadovaných vstupů v jediné sekvenci. Tato metoda zajišťuje konstantní a současně minimální časovou odchylku mezi jednotlivými kanály bez ohledu na zvolenou vzorkovací frekvenci.

## 5.2. Programování

V režimu programování lze na obvody scanovací logiky pohlížet jako na standardní nepřímo adresovanou paměť RAM s kapacitou 8x 4 bity.

Registrem ScanReg je v jedné I/O operaci současně zvolena požadovaná paměťová buňka (významné tři bity) a přenášena požadovaná data do registru scanovací logiky (významné čtyři bity). Platný rozsah a formát dat byl uveden v příslušné kapitole při popisu jednotlivých registrů.

## 5.3. Činnost v průběhu měření

V průběhu měření scanovací obvody karty při každém startu sekvence načítají parametry z paměti počínaje adresou "0" vzestupně až do adresy posledního kanálu (počet kanálů v sekvenci je definován stavem registru ScanAdrReg). Po odměření posleního kanálů je adresový čítač scanovacích parametrů nastaven na hodnotu "0".

## 5.4. Příklad programové obsluhy

Přestože je více možností programování scanovací logiky (parametry lze programovat v libovolném pořadí nebo lze modifikovat pouze některé z parametrů), lze doporučit postup znázorněný na uvedeném příkladu.

Příklad - sekvence pěti vstupů v pořadí AIN0 (±5V), AIN2 (±5V), AIN3 (±1V), AIN6 (±1V) a AIN7 (±5V):

Po naprogramování sekvence podle uvedeného postupu bude měřen vstup AIN0 jako první a vstup AIN7 jako poslední, sekvence je odměřena vcelku při jediném spouštěcím pulsu.

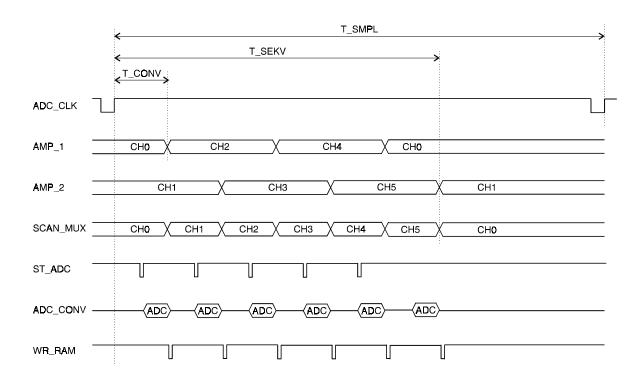

Časové poměry scanovací sekvence jsou zakresleny v diagramu Obr.11.

Jak vyplývá z uvedeného, je nutné při programování scanovacích parametrů dodržet kontinuitu adres a v registru ScanReg ponechat adresu posledního měřeného kanálu.

## 6. Popis taktovacích generátorů

## 6.1. Úvod

Karta PCA-1248 je osazena krystalovým oscilátorem 10MHz a jedním řadičem typu 82C54 obsahujícím tři 16-bitové čítače/časovače.

Vzhledem k obecné znalosti programování tohoto obvodu a současně omezeným možnostem jeho využití v jiné funkci než taktovacích generátorů, není kompletní popis tohoto obvodu v příručce zařazen a tato kapitola je věnována jedinému využitelnému pracovnímu režimu.

## 6.2. Zapojení taktovacích generátorů

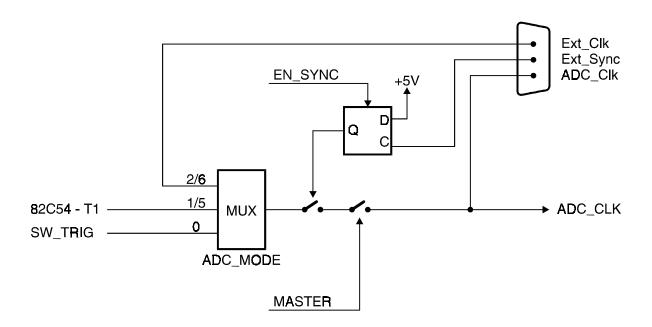

Obvodové řešení taktovacích generátorů je zakresleno na obrázku Obr.1. Ze schematu je zřejmé, že čítač T0 plní funkci generátoru signálu pro spo

Ze schematu je zřejmé, že čítač T0 plní funkci generátoru signálu pro spouštění A/D převodníku karty. Čítače T1 a T2 pracují v kaskádním zapojení ve funkci čítače ukončujícího záznam dat po naměření požadovaného počtu vzorků po detekci synchronizační události.

Všechny tři čítače jsou 16-bitové a umožňují nastavení dělicího poměru 2÷65536.

Děličku lze programovat buď na hodnotu v rozsahu 2÷65535, tzn. číslem rovným dělicímu poměru, nebo lze programováním čítače na hodnotu "0" dosáhnout dělicího poměru 65536.

## 6.3. Programování taktovacích generátorů

Prvním konfiguračním krokem je nastavení vhodných pracovních módů čítačů; vzhledem k požadované funkci je potřebným módem programovatelná dělička frekvence v módu 3 pro časovač T0 a dělička v módu 2 pro časovače T1 a T2. Z dalších možných voleb je upřednostněn režim postupného programování nižšího a vyššího byte a binární forma čítání.

Konfigurace je provedena symbolickými příkazy:

```

WR (Base+3) 36_{H} {pracovní mód čítače T0} WR (Base+3) 74_{H} {pracovní mód čítače T1} WR (Base+3) 84_{H} {pracovní mód čítače T2}

```

Po úvodní konfiguraci lze do jednotlivých čítačů naprogramovat požadovaný dělicí poměr, např. pro vzorkovací frekvenci A/D převodníku 100kHz a počet vzorků po detekované události na 1001, tzn. děličky 10, 50, 19 (počet vzorků = T1\*T2+1).

```

{čítač T0 - dělička 10 - LSB}

WR (Base+0)

10

WR (Base+0)

0

{čítač T0 - dělička 10 - MSB}

WR (Base+1)

50

{čítač T1 - dělička 50 - LSB}

{čítač T1 - dělička 50 - MSB}

WR (Base+1)

0

20

{čítač T2 - dělička 20 - LSB}

WR (Base+2)

WR (Base+2)

0 "

{čítač T2 - dělička 20 - MSB}

```

rev. 04.2000 I - 12

## 7. Popis řadiče přerušení

## 7.1. Úvod

Karta PC-1248 je vybavena programovatelnou logikou přerušení s jedním zdrojem a osmi IRQ kanály sběrnice ISA. Protože volba IRQ je omezena pouze na výběr volného kanálu přerušení, následující odstavce budou věnovány pouze volbě zdroje přerušení s ohledem na praktické využití.

Obvody přerušení mají praktický význam pouze v režimech spouštění časovačem nebo externím signálem v kombinaci se synchronizační logikou, tzn. nastaveným počtem vzorků po události.

## 7.2. Zdroje přerušení

Obvody scanovací logiky umožňují vyvolat přerušení po dokončení celého záznamu, tzn. po naměření definovaného počtu vzorků po detekci synchronizační události.

K volbě IRQ kanálu a současně i povolení generování přerušení (volbou platného IRQ kanálu) je určen registr IRQReg.

V případě volby platného IRQ kanálu je přerušení vyvoláno dokončením měření současně s nastavením příznaku EOC v registru StatusReg.

K nulování požadavku o přerušení a současně i příznaku EOC dochází automaticky při přepnutí obvodů do režimu přenosu dat (MODE=0, viz popis CWReg).

rev. 04,2000 I - 13

## 8. Popis obvodů lokální sběrnice

## 8.1. Úvod

Karta PC-1248 je vybavena portem pro externí spouštění a taktování A/D převodníku a současně i pro vzájemnou synchronizaci všech PC karet v systému; signály sběrnice jsou vyvedeny na konektor Cannon9.

Obvodové řešení je zakresleno na obrázku Obr.12.

## 8.2. Externí signály

Lokální sběrnice karet PCA-1248 podporuje externí signály Ext\_Clk pro vnější spouštění A/D převodníku a Ext\_Sync synchronizaci měření detekcí vnější události. Oba externí signály pracují s úrovněmi TTL a jsou aktivní na náběžnou hranu, tzn. přechod z logické úrovně L do úrovně H.

## 8.3. Řídicí signály

Lokální sběrnice karet PCA-1248 podporuje jeden řídicí signál generovaný interními obvody karty; ADC\_Clk je výsledným signálem pro spouštění A/D převodníku. Rozdíl oproti signálům popsaným v předešlém odstavci je patrný ze blokového schematu.

#### Důležité upozornění.

Řídicí signály mohou být aktivovány pouze u jedné karty v celém systému jedné lokální sběrnice (tzv. master) a současně musí být aktivovány i v případě samostatně provozované karty.

rev. 04,2000

## 9. Popis digitálních vstupů a výstupů

## 9.1. Úvod

Karta PCA-1248 obsahuje 8 vstupních kanálů a 8 kanálů výstupních; signály obou portů jsou umístěny na dvou konektorech DIL10.

V případě potřeby lze použít redukční kabel DIG-14, který převede signály z obou konektorů DIL10 na 2x Cannon9.

### 9.2. Zapojení vstupů

Pro realizaci vstupů bylo využito obvodů technologie HCTMOS. Jejich výhodné vlastnosti (vysoká vstupní impedance a zanedbatelný vstupní proud, ochranné diody) byly využity pro přepěťovou ochranu do ±24V.

Protože klidový stav vstupů odpovídá logické úrovni H (ošetřeno rezistory  $10k\Omega$  proti napětí +5V), lze je použít i pro připojení signálů typu "otevřený kolektor".

## 9.3. Zapojení výstupů

Pro realizaci výstupů bylo využito obvodů technologie HCMOS. Pro jejich výhodné vlastnosti (vysoký výstupní proud a zanedbatelný napěťový úbytek) je lze využít pro přímé buzení LED, optronů, popř. i miniaturních relé  $5\text{V}/500\Omega$ .

rev. 04.2000 I - 15

## 10. Popis programové obsluhy

## 10.1. Úvod

Struktura karty PCA-1248 a tedy i její programová obsluha je zcela odlišná od obvyklých výrobků. Základní charakteristika je shrnuta v následujících bodech:

- 1) Obvody A/D převodníku jsou určeny zejména pro režim spouštění časovačem nebo externím signálem; alternativně však umožňují i spouštění programové.

- 2) Ve všech režimech spouštění je celý dostupný paměťový prostor vyhrazen jako kruhový zásobník, data jsou postupně zapisována v pořadí naprogramovaném ve scanovací logice.

- 3) Měření je ukončeno po provedení zvoleného počtu sekvencí nebo jej lze ukončit kdykoliv programově.

- 4) Data lze přenést do operační paměti pomocí metody nepřímé adresace nebo výrazně rychleji s využitím režimu autoinkrementace.

- 5) Podpora karty PCA-1248 je jednodušší než u klasických karet; periodické spouštění a zejména pak požadavek na rychlý přenos dat zcela odpadá.

## 10.2. Struktura paměti RAM

Základní paměť 2MB je organizována do struktury 1M x 16 bitů a umožňuje tedy záznam 1.048.576 údajů z A/D převodníku. Celá paměť je adresována 20-bitovým čítačem, který je v pracovním režimu měření inkrementován vždy po dokončení zápisového pulsu. Proto je ukazatel paměti vždy nastaven na adresu následující po poslední aktualizované buňce paměti.

V případě osazení karty násuvným modulem XM-1248 je kapacita paměti rozšířena na 8MB a celá paměť je pak adresována 22-bitovým čítačem.

V režimu přenosu naměřených dat je RAM přístupná prostřednictvím registru RamDataReg a adresový čítač je dostupný prostřednictvím registru RAMAdrReg; nevyužité bity jsou při zápisu nevýznamné, při čtení jsou trvale v úrovni L. Kromě možnosti přímého zápisu adresy RAM do registru RAMAdrReg umožňuje karta automatickou inkrementaci adresy při čtení, resp. zápisu do paměti a tím zásadně zefektivnit přenos naměřených dat do operační paměti počítače (viz popis CWReg). Výchozí adresou při zahájení měření je poslední stav 20-bitového čítače definovaný registrem RAMAdrReg; do této buňky jsou pak uložena data z prvního měřeného kanálu první sekvence. K inkrementaci čítače dochází bezprostředně po ukončení každého zápisu a stav čítače (přístupný registry RAMAdrReg) vždy ukazuje na buňku, do které budou zapsána následující data.

#### 10.3. Režim spouštění časovačem

Podporu tohoto režimu lze považovat u karty PCA-1248 za základní.

Při programové obsluze je nutné dodržet tento postup:

- 1) Naprogramovat scanovací logiku prostřednictvím registru ScanReg.

- 2) Inicializovat všechny časovače do odpovídajícího pracovního módu.

- 3) Nastavit vzorkovací frekvenci naprogramováním čítače T0.

- 4) Nastavit počet měřených sekvencí do čítačů T1 a T2. (počet sekvencí = T1 \* T2+1, kde T1 a T2 jsou data programovaná do čítačů)

rev. 04,2000

- 5) Nastavit počáteční adresu záznamu.

- 6) Spustit měření zvolením vhodného režimu.

- 7) Ukončit měření a načíst data z paměti RAM.

Čítače T1 a T2 jsou zapojeny do kaskády (na vstup CLK čítače T1 jsou přivedeny spouštěcí pulsy sekvence (časovač, externí i programové). Po dosažení požadovaného počtu sekvencí dojde k zablokování startovacích pulsů.

#### 10.4. Režim spouštění externím signálem

Podpora tohoto režimu je totožná s režimem spouštění časovačem, rozdílem je pouze absence programování čítače T0.

Při měření je nutné technickými prostředky zajistit, aby frekvence externích pulsů nepřekročila hranici odpovídající naprogramované sekvenci; karta nedisponuje žádnými prostředky pro detekci tohoto jevu!

#### Důležité upozornění.

Všechny tři čítače musí být vždy naprogramovány do odpovídajícího pracovního módu a to i v případě, že nebudou při měření využity.

### 10.5. Režim programového spouštění

Při této metodě spouštění A/D převodníku postačuje z předešlého postupu pouze naprogramovat a inicializovat scanovací logiku; po nastavení počáteční adresy RAM pak lze programovými povely spouštět měřicí sekvence.

Protože celé časování je v plné režii aplikačního programu, mohou být naměřená data přenášena po jednotlivých měřeních, po blocích i po ukončení celého záznamu.

#### 10.6. Přenos dat do operační paměti

Při opakování sekvence je adresa s každým zápisem inkrementována (20/22-bitový čítač vpřed) až do vyčerpání celého adresového prostoru a následující data přepisují nejstarší naměřený vzorek.

V případě dlouhodobých měření, kdy dochází k opakovanému zapisu do RAM (např. při využití synchronizační logiky), je nutné při načítání dat do operační paměti počítače využít stavu adresového čítače při ukončení měření (ukazuje na buňku následující po posledním zapsaném vzorku) a pomocných příznaků FRST a TRG (viz popis registru RAMDataReg).

Vlastní přenos dat lze nejjednodušeji realizovat pomocí funkce autoinkrementace adresy datové paměti při operaci čtení; při přenosu dat je pak nová adresa generována automaticky vždy po dokončení I/O operace.

Pro odlišení platného obsahu paměti od dat zachovaných z předešlých měření může aplikační program celý obsah paměti zaplnit vhodnou konstantou, např. FFFF.

rev. 04.2000 I - 17

|         |         | bázová I/O adresa |         |         |                  |

|---------|---------|-------------------|---------|---------|------------------|

| SW1 - 2 | SW1 - 3 | SW1 - 4           | SW1 - 5 | SW1 - 6 | (BASE)           |

| ON      | ON      | ON                | ON      | ON      | 200 <sub>H</sub> |

| ON      | ON      | ON                | ON      | OFF     | 210 <sub>H</sub> |

|         |         |                   |         |         |                  |

| OFF     | ON      | ON                | ON      | ON      | 300 <sub>H</sub> |

| OFF     | ON      | ON                | ON      | OFF     | 310 <sub>H</sub> |

|         |         |                   |         |         |                  |

| OFF     | OFF     | OFF               | OFF     | ON      | 3E0 <sub>H</sub> |

| OFF     | OFF     | OFF               | OFF     | OFF     | 3F0 <sub>н</sub> |

Tab.1. SW1 - volba bázové adresy karty.

| Počáteční adresa | Koncová adresa   | I/O zařízení                       |

|------------------|------------------|------------------------------------|

| 200 <sub>H</sub> | 207 <sub>H</sub> | adapter pro hry                    |

| 278 <sub>H</sub> | 27F <sub>H</sub> | 2. tiskárna                        |

| 2F8 <sub>H</sub> | 2FF <sub>H</sub> | 2. adapter asynchronní komunikace  |

| 300 <sub>H</sub> | 31F <sub>H</sub> | prototypová deska                  |

| 360 <sub>H</sub> | 36F <sub>H</sub> | rezerva                            |

| 378 <sub>H</sub> | 37F <sub>H</sub> | 1. tiskárna                        |

| 380 <sub>H</sub> | 38F <sub>H</sub> | synchronní komunikace SDLC         |

| 3A0 <sub>H</sub> | 3AF <sub>H</sub> | synchronní komunikace BSC          |

| 3B0 <sub>H</sub> | 3BF <sub>H</sub> | monochromatický display + tiskárna |

| 3C0 <sub>H</sub> | 3CF <sub>H</sub> | rezerva                            |

| 3D0 <sub>H</sub> | 3DF <sub>H</sub> | barevný display                    |

| 3F0 <sub>H</sub> | 3F7 <sub>H</sub> | řadič disket                       |

| 3F8 <sub>H</sub> | 3FF <sub>H</sub> | 1. adapter asynchronní komunikace  |

Tab.2. Seznam standardních adres I/O zařízení.

| funkce           | PIN | PIN | funkce            |

|------------------|-----|-----|-------------------|

| A GND            | C13 | 005 | 1 1 1             |

| A GND            | C12 | C25 | Analog In 0       |

| A GND            | C11 | C24 | Analog In 1       |

| A GND            | C10 | C23 | Analog In 2       |

|                  |     | C22 | Analog In 3       |

| A GND            | C9  | C21 | Analog In 4       |

| A GND            | C8  | C20 | Analog In 5       |

| A GND            | C7  |     |                   |

| A GND            | C6  | C19 | Analog In 6       |

| A GND            | C5  | C18 | Analog In 7       |

| A GND            |     | C17 |                   |

|                  | C4  | C16 | Analog Out 0      |

|                  | C3  | C15 | GND               |

| GND              | C2  |     |                   |

| +5V (500mA max.) | C1  | C14 | +12V (500mA max.) |

Tab.3. Zapojení vývodů konektoru Cannon 25.

A GND společná svorka analogových vstupů a výstupů GND společná svorka napájecích napětí +5V a +12V (proudový odběr max. 0,5A)

| funkce           | PIN | PIN      | funkce   |

|------------------|-----|----------|----------|

| GND              | C5  | C9       |          |

| ADC_Clk          | C4  | C9<br>C8 | Evt Suno |

| Ext_Clk          | C3  | C8       | Ext_Sync |

|                  | C2  |          |          |

| +5V (500mA max.) | C1  | C6       |          |

Tab.4. Zapojení vývodů konektoru Cannon 9.

GND společná svorka všech signálů i napájecího napětí (proudový odběr max. 0,5A)

| funkce       | PIN | PIN | funkce       |

|--------------|-----|-----|--------------|

| DIN0 / DOUT0 | D1  | D2  | DIN1 / DOUT1 |

| DIN2 / DOUT2 | D3  | D4  | DIN3 / DOUT3 |

| DIN4 / DOUT4 | D5  | D6  | DIN5 / DOUT5 |

| DIN6 / DOUT6 | D7  | D8  | DIN7 / DOUT7 |

| GND          | D9  | D10 | +5 <i>V</i>  |

Tab.5. Zapojení vývodů konektorů DIL10.

| funkce        | PIN | PIN | funkce       |

|---------------|-----|-----|--------------|

| GND           | C5  |     |              |

| DING / DOLLTS | C4  | C9  | DIN7 / DOUT7 |

| DIN6 / DOUT6  | C4  | C8  | DIN5 / DOUT5 |

| DIN4 / DOUT4  | C3  |     |              |

| DIN2 / DOUT2  | C2  | C7  | DIN3 / DOUT3 |

| DINZ/DOOTZ    | 02  | C6  | DIN1 / DOUT1 |

| DIN0 / DOUT0  | C1  |     | 2, 200       |

Tab.6. Zapojení vývodů konektorů Cannon 9 (DIG-14).

| ADRESA   | zápis (WR) | čtení (RD) |  |  |

|----------|------------|------------|--|--|

| Base + 0 |            |            |  |  |

| Base + 1 | 82C54      |            |  |  |

| Base + 2 |            | 301        |  |  |

| Base + 3 | 7          |            |  |  |

| Base + 4 | DACReg     |            |  |  |

| Base + 5 | SyncReg    |            |  |  |

| Base + 6 |            |            |  |  |

| Base + 7 | IRQReg     |            |  |  |

| Base + 8 | RAMD       | ataReg     |  |  |

| Base + 9 | ADCTrigReg |            |  |  |

| Base + A | ScanReg    |            |  |  |

| Base + B | CWReg      | StatusReg  |  |  |

| Base + C |            |            |  |  |

| Base + D | RAMA       | AdrReg     |  |  |

| Base + E | 7          |            |  |  |

| Base + F | DigOutReg  | DigInReg   |  |  |

Tab.7. Vnitřní struktura adresového prostoru karty.

Obr.1. Vnitřní struktura karty PCA-1248.

rev. 04.2000 III - 1

Obr.2. Rozmístění důležitých prvků na kartě PCA-1248.

- SW1 volba bázové adresy karty

P1 kompenzace napěťové nesymetrie zesilovače 1. kanálu (při zesílení 5x)

P2 kompenzace napěťové nesymetrie zesilovače 2. kanálu (při zesílení 5x)

P3 kompenzace celkového ofsetu 1. kanálu (při zesílení 1x)

P4 kompenzace celkového ofsetu 2. kanálu (při zesílení 1x)

P5 kalibrace rozsahu A/D převodníku (±5V)

- Některé trimry jsou osazovány na desku pouze v případě zakázkových úprav.

Obr.3. Rozmístění vývodů na konektoru Cannon 25.

Obr.4. Rozmístění vývodů na konektoru Cannon 9.

Obr.5. Rozmístění vývodů na konektoru DIL 10.

Obr.6. Propojovací kabel s PC štítkem DIG-14, rozmístění portů na konektorech.

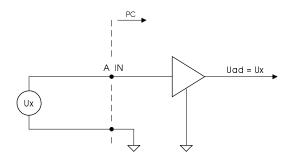

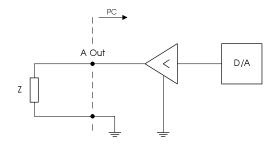

#### Obr.7. Připojení analogového vstupu karty.

#### Obr.8. Připojení analogového výstupu karty.

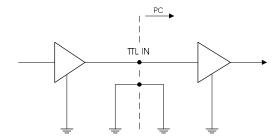

#### Obr.9. Připojení digitálních vstupů karty.

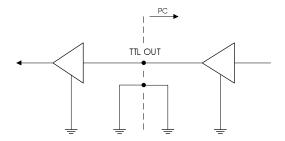

Obr.10. Připojení digitálních výstupů karty.

#### Obr.11. Časové poměry scanovací sekvence.

| ADC_CLK  | signál pro spouštění měřicí sekvence                                                                            |

|----------|-----------------------------------------------------------------------------------------------------------------|

|          | • odvozen od časovače, externího signálu, popř. programově                                                      |

|          | • je totožný se stejnojmenným signálem lokální sběrnice                                                         |

| AMP_1    | představuje signál 1. analogového kanálu                                                                        |

| AMP_2    | představuje signál 2. analogového kanálu                                                                        |

| SCAN_MUX | představuje výsledný signál přiváděný do A/D převodníku                                                         |

| ST_ADC   | signál pro spuštění A/D převodu v rámci měřicí sekvence                                                         |

| ADC_CONV | představuje vlastní činnost A/D převodníku                                                                      |

| WR_RAM   | signál pro přenos dat z A/D převodníku do FIFO                                                                  |

| T_CONV   | čas potřebný pro odměření jednoho kanálu<br>= 1 μs                                                              |

| T_SEKV   | čas nutný pro provedení celé sekvence<br>= NrCH * T_CONV - 0,1 μs<br>kde NrCH je počet kanálů v měřicí sekvenci |

| T_SMPL   | perioda spouštění sekvence<br>T_SMPL <sub>MIN</sub> = NrCH * T_CONV                                             |

Zkrácení prvního cyklu z 1,0 µs na 0,9 µs je nutné pro zajištění minimální periody spouštění sekvence jako celistvého násobku 1,0 µs.

Obr.12. Zapojení obvodů lokální sběrnice.