# PCA-1288

8x 12-bit. ADC 8x 12-bit. DAC CNT, IRQ, DIO

# Důležité upozornění!

Při zacházení s kartou dbejte zásad mani pulace s obvody citlivými na poškození elektrostatickým nábojem.

Instalaci provádějte zásadně při vypnutém počítači a vždy odpojte síťový kabel a přívodní vodiče karty!

Při nedodržení uvedených pravi del může dojít k trvalému poškození citlivých obvodů PC karty nebo celého počítače.

Uži vatelská příručka a její součásti jsou autorským dílem chráněným ustanovením zákona č. 35/1965 Sb. o dílech li terárních, vědeckých a uměleckých (Autorský zákon) ve znění zákona č. 89/1990 Sb., zákona č. 468/1991 Sb., zákona č. 318/1993 Sb., zákona č. 237/1995 Sb. a zákona č. 86/1996 Sb.

Všechna jména a názvy použi té v textu mohou být chráněnými známkami nebo obchodními názvy výrobků příslušných firem.

© 1994÷2000 TEDIA spol. s r. o.

Záruční a pozáruční servis:

TEDIA spol. s r. o., Zábělská 12, 312 11 Plzeň 12

telefon: 019 7478168 fax: 019 7478169 e-mail: tedia@tedia.cz internet: http://www.tedia.cz

# Obsah

| 1.                                           | Úvodní popis<br>Charakteristika                                                                                                                                         | I - 1                                              |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 2.1.<br>2.2.<br>2.3.<br>2.4.<br>2.5.<br>2.6. | Technické parametry A/D převodník D/A převodníky Čítače Obvody přerušení Digitální porty Ostatní údaje                                                                  | I - 2<br>I - 2<br>I - 2<br>I - 2<br>I - 2<br>I - 3 |

| 3.1. 3.2. 3.3. 3.4. 3.5.                     | Instalace karty<br>Úvod<br>Nastavení bázové adresy<br>Vlastní instalace<br>Rozmístění spínačů a konektorů<br>Zapojení konektorů                                         | I - 4<br>I - 4<br>I - 4<br>I - 4<br>I - 4          |

| 4.1.<br>4.2.                                 | Základní informace<br>Úvod<br>Terminologie                                                                                                                              | I - 5<br>I - 5                                     |

| 5.1. 5.2. 5.3. 5.4. 5.5. 5.6. 5.7.           | Struktura adresového prostoru karty Popis adresového dekodéru CWReg STSReg RAMReg ADRReg DigOutReg DigInReg                                                             | I - 6<br>I - 6<br>I - 7<br>I - 7<br>I - 7<br>I - 7 |

| 6.1.<br>6.2.<br>6.3.                         | Popis digitálních vstupů a výstupů<br>Úvod<br>Zapojení vstupů<br>Zapojení výstupů                                                                                       | I - 8<br>I - 8<br>I - 8                            |

| 7.1.<br>7.2.<br>7.3.<br>7.4.                 | Popis firmware<br>Úvod<br>Obsah DPRAM - přehled<br>Popis činnosti firmware po startu<br>Popis činnosti firmware ve výkonné smyčce                                       | I - 9<br>I - 9<br>I - 10<br>I - 10                 |

| 8.1.<br>8.2.<br>8.3.<br>8.4.<br>8.5.         | Popis programové podpory<br>Úvod<br>Čtení obsahu základního datového bloku<br>Řízení analogových výstupů<br>Řízení čítačů<br>Programová obsluha vyrovnávacích zásobníků | I - 11<br>I - 11<br>I - 11<br>I - 11<br>I - 12     |

| Přílol                                       | nv:                                                                                                                                                                     |                                                    |

Příloha II - tabulky Příloha III - obrázky

# 1. Úvodní popis

### 1.1. Charakteristika

PCA-1288 je řada multifunkčních PC karet moderní konstrukce ze stavebnice karet "CHALLENGE SERIE".

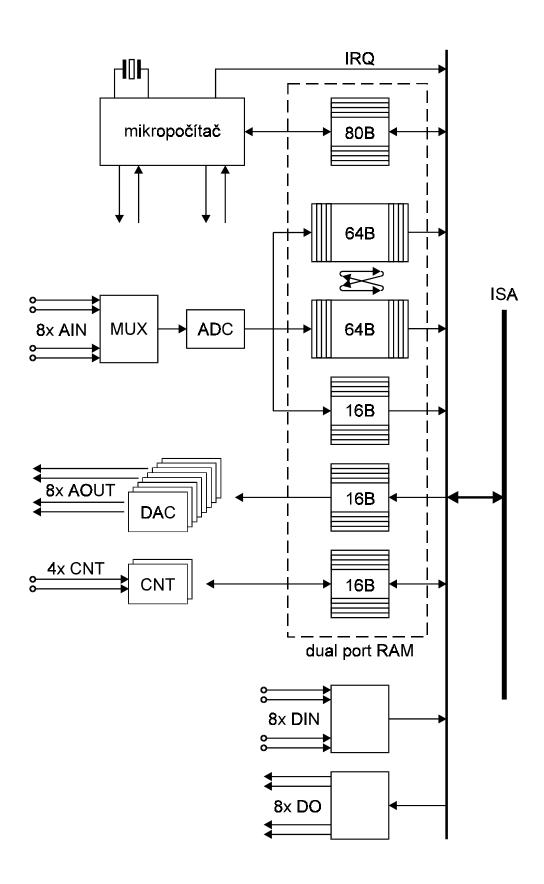

K přednostem karet patří jednoduchá programová konfigurovatelnost většiny parametrů. Při vlastní instalaci karty do počítače je nutné hardwarově nastavit pouze bázovou adresu karty; všechny ostatní funkce karty jsou ovládány plně softwarově. Vnitřní obvodová struktura karet řady PCA-1288 a celkový pohled na desky jsou zakresleny na obrázcích Obr.1. a Obr.2.

#### Svojí koncepcí je určena zejména pro:

- řídicí systémy s více analogovými výstupy

- měření unifikovaných signálů 10V/20mA se vzorkovacím kmitočtem do 500Hz

#### Vlastní karta obsahuje:

- 8 analogových vstupů s rozlišením 12 bitů

- 8 analogových výstupů s rozlišením 12 bitů

- 4 čítače externích událostí (dva "rychlé" a dva "pomalé")

- logiku přerušení (IRQ2 ÷ IRQ11)

- 16 digitálních kanálů (8 vstupů a 8 výstupů)

# 2. Technické parametry

# 2.1. A/D převodník

počet vstupů: 8 S.E. rozlišení A/D převodníku: 12 bitů

vstupní rozsah: 0÷10V (PCA-1288A) 0÷5V (PCA-1288B)

0÷5V (PCA-1288B)

vstupní impedance:  $40k\Omega$  typ. (PCA-1288A)

$20k\Omega$  typ. (PCA-1288B)

maximální vstupní napětí: ±24V

$\pm 100V$  (10ms max.)

Při překročení maximálního vstupního napětí může dojít k trvalému poškození obvodů karty.

# 2.2. D/A převodníky

počet výstupů: 8

rozlišení D/A převodníků: 12 bitů

výstupní rozsah: 0÷10V (PCA-1288A)

0÷5V (PCA-1288B)

doba ustálení analogového výstupu: 2ms max.  $(\pm 0,1\%)$  výstupní impedance:  $10\Omega$   $(\pm 1\%)$

zatěžovací impedance:  $500\Omega$  min.

Výstupy D/A převodníků jsou odolné proti trvalému zkratu proti GND.

Přivedením vnějšího napětí mimo pracovní rozsah dojde k nevratnému poškození obvodů.

### 2.3. Čítače

počet čítačů: dva "rychlé" a dva "pomalé"

rozlišení čítačů: 32 bitů

pracovní úrovně: TTL/HCMOS

pracovní frekvence: 100 Hz max. (CNT0, CNT1) 100 kHz max. (CNT2, CNT3)

Dosažení mezní frekvence vyžaduje signál se střídou 50%. Čítače jsou odolné proti přepětí ±24V.

# 2.4. Obvody přerušení

zdroj přerušení: DRDY (konec zápisu bloku) IRQ kanál: IRQ2 ÷ IRQ11 (voleno programově)

# 2.5. Digitální porty

počet vstupů: 8 (TTL komp.) počet výstupů: 8 (TTL komp.) zatěžovací impedance výstupů:  $500\Omega$  min. (viz pozn.)

Vstupní porty jsou odolné proti přepětí ±24V. Výstupní digitální porty jsou odolné proti trvalému zkratu proti GND; přivedením napětí mimo rozsah 0÷5V dojde k nevratnému poškození obvodů.

# 2.6. Ostatní údaje

typ sběrnice: ISA

I/O adresa:  $200_{\rm H} \div 3FC_{\rm H}$  (128 intervalů)

délka intervalu obsazených adres: 4

napájecí napětí: +5V (200mA max.)

+12V (50mA max.) -12V (50mA max.)

výstup zdrojů +5V / +12V: 2x 500mA max. rozměry desky: cca 100x158mm EMC: ČSN EN 55022

ČSN EN 50081-1 ČSN EN 50082-1

Proudový odběr z napájecího zdroje je uveden pro všechny výstupy v nezatíženém stavu.

# 3. Instalace karty

# 3.1. Úvod

Při výrobě bylo dbáno na dosažení vysoké kvality a spolehlivosti, rovněž byla věnována pozornost důkladné kontrole před expedicí. Aby nedošlo ke snížení jakosti či poškození při instalaci, doporučujeme Vám pečlivě prostudovat tuto příručku a postupovat podle uvedeného návodu.

# 3.2. Nastavení bázové adresy

Bázovou adresu PC karty lze nastavit v rozsahu 200<sub>H</sub> až 3FC<sub>H</sub>. Volba se provádí prostřednictvím osminásobného DIL přepínače DIL SW1; význam jednotlivých segmentů je vyznačen v tabulce Tab.1. Při volbě je třeba dbát, aby nedošlo ke kolizi s ostatními instalovanými I/O zařízeními. Seznam standardních zařízení umístěných v tomto intervalu adres je uveden v tabulce Tab.2.

#### 3.3. Vlastní instalace

Instalaci karty provádějte zásadně při vypnutém počítači a dodržujte zásady pro manipulaci s obvody citlivými na poškození elektrostatickým nábojem. S kartou manipulujte za okraje a nedotýkejte se prsty součástek. Nakonfigurovanou kartu zasuňte po předchozím vyjmutí krycího štítku do volné pozice pro rozšiřující desky počítače a zajistěte šroubem.

### 3.4. Rozmístění spínačů a konektorů

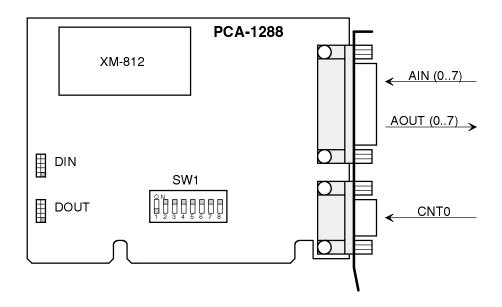

Na obrázků Obr.2. je vyznačeno rozmístění důležitých prvků na kartě; význam spínačů je zřejmý z předchozího textu, konektory budou popsány vždy v příslušných kapitolách.

### 3.5. Zapojení konektorů

Zapojení vývodů uživatelských konektorů je zakresleno na obrázcích Obr.3. až Obr.5., význam jednotlivých vývodů je popsán v tabulkách Tab.3. až Tab.5.

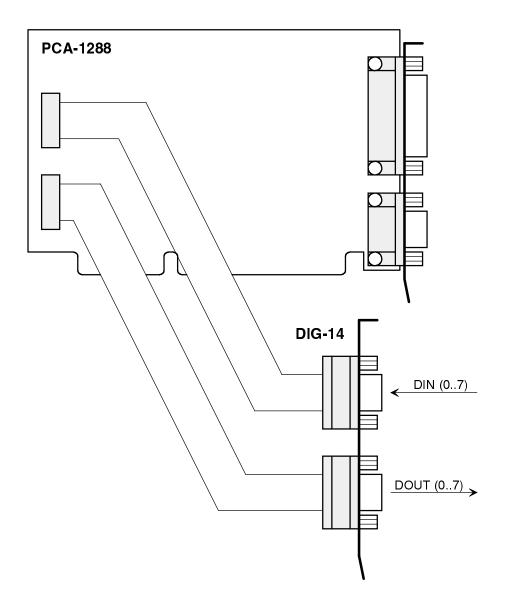

Digitální porty mohou být zpřístupněny na zadní straně skříně počítače propojovacím kabelem s PC štítkem DIG-14 (viz. Obr.6.); zapojení vývodů dvou konektorů Cannon 9 je popsáno v tabulce Tab.6.

Správné připojení k měřenému objektu je naznačené na obrázcích Obr.7. až Obr.9.

# 4. Základní informace

# 4.1. Úvod

Multifunkční PC karty klasické koncepce jsou zpravidla osazeny periferními obvody plně ovládanými z PC, tzn. počítač má ve svém adresovém prostoru přímo mapovány příslušné řídicí a datové registry.

Odlišná koncepce je využita u PC karet řady PCA-1288. Tyto multifunkční PC karty jsou osazeny řídicím mikropočítačem s implementovaným algoritmem pro obsluhu analogových vstupů a výstupů, čítačů a dalších funkcí. Komunikace s kartou proto probíhá pomocí povelů se strukturou závislou na programovém vybavení instalovaném v paměti řídicího mikropočítače.

Z uvedených důvodů lze doporučit podrobné seznámení s činností desky popsané v následujících odstavcích a kapitolách.

# 4.2. Terminologie

Základní termíny používané v dalších odstavcích příručky:

Režim desky: • deska, resp. její řídicí obvody, mohou být přepnuty do různých

funkčních režimů (RST, RUN, ...)

Povel: • je příkaz aktivující výkonné funkce

(např. zápis/čtení čítačů, nulovaní registrů, ...)

DPRAM: • dvoubránová paměť RAM

datová paměť dostupná ve stejný okamžik mikropočítači i PC

• tato paměť je využita pro řízení i přenos dat

# 5. Struktura adresového prostoru

### 5.1. Popis adresového dekodéru

Adresový dekodér umožňuje relokaci bázové adresy karty v rozsahu u 200<sub>H</sub> až 3FC<sub>H</sub>. Protože karta zabírá celkem 4 I/O adresy, lze volit jeden z 128 intervalů.

Karta obsahuje několik typů registrů:

DPRAM: • registry dvoubránové paměti (komunikace s mikropočítačem)

(RAMReg, ADRReg)

řídicí: • registr pro volbu režimu karty a volbu kanálu přerušení

(CWReg, RSTReg)

DIO: • slouží k přímému řízení digitálních portů (vstupní i výstupní)

(DigInReg, DigOutReg)

Struktura registrů v adresovém prostoru je přehledně uvedena v tabulce Tab.6. a částečně také zakreslena na obrázku Obr.2.

### 5.2. CWReg

(WR, Base+3)

Řídicí registr karty slouží k volbě pracovních režimů (jejich podrobný popis je uveden v dalších kapitolách) a volbě kanálu přerušení.

Registr je po resetu nebo zapnutí počítače vynulován.

Struktura registru a význam jednotlivých bitů je následující:

| D7 | D6 | D5 | D4 | D3    | D2 | D1   | D0 |

|----|----|----|----|-------|----|------|----|

|    |    | ?Q |    | INTEN |    | MODE |    |

MODE • volba režimu PC karty

000 RST reset mikropočítače PCA-1288 100 RUN provozní režim

INTENpovolení přerušení

o přerušení PC sběrnice je blokováno

1 přerušení PC sběrnice je povoleno

IRQ • volba kanálu přerušení

0010 IRQ2 0011 IRQ3 .....0111 IRQ7 1010 IRQ10 1011 IRQ11

RSRV • rezerva

INTEN slouží současně k nulování požadavku přerušení (sekvence 1-0-1).

# 5.3. STSReg

(RD, Base+3)

Prostřednictvím této I/O adresy je zpřístupněn stavový registr signalizující aktivní signál IRQ. Tento signál je nastavován bez ohledu na zvolený kanál IRQ a lze jej využít i pro softwarový pooling (ve spojení s bitem INTEN, viz CWReg).

| D7   | D6 | D5 | D4 | D3  | D2 | D1   | D0 |

|------|----|----|----|-----|----|------|----|

| RSRV |    |    |    | INT |    | RSRV |    |

INT

indikace požadavku přerušení

0 karta má neaktivní signál IRQ

1 karta má aktivní signál IRO

RSRV • rezerva

# 5.4. RAMReg

(RD/WR, Base+0)

Prostřednictvím této I/O adresy je zpřístupněn celý adresový prostor dvoubránové paměti. Protože obsah registru představuje přímo data paměťové buňky DPRAM, je popis vnitřní struktury a význam uveden v kapitole věnované programové obsluze.

# 5.5. ADRReg

(WR, Base+1)

Prostřednictvím tohoto registru je adresován celý prostor dvoubránové paměti. Protože obsah registru představuje přímo adresu pamětové buňky RAM v celém rozsahu 0÷255, není další popis struktury registru potřebný.

### 5.6. DigOutReg

(WR, Base+2)

Tento registr plní funkci výstupního digitálního portu; význam jednotlivých bitů je zřejmý ze struktury registru a zapojení konektoru portu. Registr je po resetu, resp. zapnutí počítače vynulován.

Struktura registru:

| D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

|-------|-------|-------|-------|-------|-------|-------|-------|

| DOUT7 | DOUT6 | DOUT5 | DOUT4 | DOUT3 | DOUT2 | DOUT1 | DOUT0 |

### 5.6. DigInReg

(RD, Base+2)

Tento registr plní funkci vstupního digitálního portu; význam jednotlivých bitů je zřejmý ze struktury registru a zapojení konektoru portu. Struktura registru:

| D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0   |

|------|------|------|------|------|------|------|------|

| DIN7 | DIN6 | DIN5 | DIN4 | DIN3 | DIN2 | DIN1 | DINO |

# 6. Popis digitálních vstupů a výstupů

# 6.1. Úvod

PC karty řady PCA-1288 obsahují 8 vstupních kanálů a 8 kanálů výstupních; signály obou portů jsou umístěny na dvou konektorech DIL10.

V případě potřeby lze použít redukční kabel DIG-14, který převede signály z obou konektorů DIL10 na 2x Cannon9 (viz. Obr.6.).

# 6.2. Zapojení vstupů

Pro realizaci vstupů bylo využito obvodů technologie HCTMOS. Jejich výhodné vlastnosti (vysoká vstupní impedance a zanedbatelný vstupní proud, ochranné diody) byly využity pro přepěťovou ochranu do ±24V.

Protože klidový stav vstupů odpovídá logické úrovni H (ošetřeno rezistory  $10k\Omega$  proti napětí +5V), lze je použít i pro připojení signálů typu "otevřený kolektor".

# 6.3. Zapojení výstupů

Pro realizaci výstupů bylo využito obvodů technologie HCMOS. Pro jejich výhodné vlastnosti (vysoký výstupní proud a zanedbatelný napěťový úbytek) je lze využít pro přímé buzení LED, optronů, popř. i miniaturních relé  $5V/500\Omega$ .

# 7. Popis firmware

# 7.1. Úvod

Dále uvedený popis odráží stav firmware verze 1.08; nově implemetované funkce pak budou dokumentovány podle jejich rozsahu v dodatcích uživatelské příručky v souborech na doprovodné disketě nebo v samostatné příručce.

Další popis této kapitoly je vztažen k pracovnímu režimu desky "RUN", tzn. stavu po spuštění firmware.

# 7.2. Obsah DPRAM - přehled

Pro komunikaci s mikropočítačem karty, tzn. přenos dat a řídicích povelů, slouží dvoubránová paměť.

Dvoubránová paměť obsahuje 256 registrů rozdělených do čtyř bloků po 64 registrech. Jednotlivé bloky mají následující funkce:

| 0÷63    | obsahuje okamžitá data všech vstupních portů                        |

|---------|---------------------------------------------------------------------|

|         | (tzn. data průběžně aktualizovaná při každém cyklu)                 |

| 64÷127  | obsahuje data analogových výstupů, řídicí povely a stavové příznaky |

| 128÷255 | vyrovnávací zásobník vstupních dat (analogových vstupů, čítačů,)    |

|         | rozdělený do dvoufázově zaplňovaných bloků BLK 0 a BLK 1            |

Přesný popis struktura a význam registrů dvoubránové paměti je popsána v tabulce Tab.7. a následujících odstavcích.

| AINx      | 16-bitové registry analogových vstupů (data v přímém binárním kódu, tzn. $0000_{ m H} \sim 0{ m V}$ a $0{ m FFF}_{ m H} \sim 5/10{ m V}$ ) |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| CNTx      | 32-bitové registry čítačů                                                                                                                  |

| CNT_IN    | aktuální stav vstupů čítačů CNT0÷CNT3 - logická úroveň L nebo<br>H                                                                         |

|           | (významné 4 nejnižšší bity, každý bit obsahuje stav jednoho vstupu)                                                                        |

| CNT_ON    | provozní čas karty (čas v milisekundách od spuštění mikropočítače)                                                                         |

| AOUTx     | 16-bitové registry analogových vstupů<br>(data v přímém binárním kódu, tzn. 0000 <sub>H</sub> ~ 0V a 0FFF <sub>H</sub> ~ 5/10V)            |

| TYP       | identifikační ASCII řetězec (např. "PCA-1288 1.08")                                                                                        |

| Ctrl_CNTx | řídicí registry čítačů                                                                                                                     |

| Ctrl_BF   | řídicí registr vyrovnávacího zásobníku                                                                                                     |

# Povel základní řídicí registr

Adr\_BF

Status

### 7.3. Popis činnosti firmware po startu

základní příznakový registr

Po startu firmware mikropočítače (tzn. po nastavení režimu RUN, viz popis CWReg) provádí řadu nezbytných inicializační kroků (nastavení perferních obvodů, nastavení obsahu dvoubránové paměti apod.)

stavový registr vyrovnávacího zásobníku

Průběh a ukončení inicializace je signálizováno registrem Povel; na začátku inicializace (cca 10µs po spuštění režimu RUN) mikropočítač nastaví registr na hodnotu 255 a po ukončení incializace je vynuluje. Po dobu inicializace nesmí být obsah dvoubránové paměti ze strany PC modifikován.

Po ukončení inicializace je většina registrů vynulována, vyjímku tvoří:

Ctrl\_BF nastaven na hodnotu 49

(tzn. každý 100ms je zaplněna jedna polovina zásobníku)

Adr\_BF registr nastaven na hodnotu 80<sub>H</sub>

TYP zapsán identifikační řetězec

# 7.4. Popis činnosti firmware ve výkonné smyčce

Obsluhu všech I/O funkcí vykonává řidicí mikropočítač v uzavřených programových smyčkách, tzv. cyklech. Délka jednoho cyklu trvá 2ms.

V každém cyklu programové smyčky mikropočítač provádí tyto operace:

#### 1. Měření osmi analogových signálů

Naměřená data jsou zapsána do interní paměti mikropočítače a v případě povolení zápisu do dvoubránové paměti rovněž do prvního bloku RAM. Měření jednotlivých vstupů jsou rovnoměrně rozložena v celém cyklu.

#### 2. Zpracování dat osmi analogových výstupů

Mikropočítač načte data z dvoubránové paměti a postupně zpracuje D/A převodníkem a osmi "sample and hold" obvody.

Generování osmi výstupních signálů je rovnoměrně rozloženo v celém cyklu.

#### 3. Zpracování dat čtyř čítačů

Data čtyř čítačů jsou zapsána do interní paměti mikropočítače a v případě povolení zápisu do dvoubránové paměti rovněž do základního bloku RAM. Přenos dat je rovnoměrně rozložen v celém cyklu.

#### 4. Generování provozního času

Mikropočítač inkrementuje stav registru CNT\_ON a v případě povolení zápisu do dvoubránové paměti přenese jeho obsah do prvního bloku RAM.

#### 5. Obsluha vyrovnávacích zásobníků

Mikropočítač vyhodnotí požadavek na vzorkovací frekvenci kontinuálního záznamu (registr Ctrl\_BF) a rozhodne, zda bude realizován přenos do vyrovnávacího zásobníku a do kterého ze dvou částí budou data zapsána. Jsou-li data do zásobníku zapisována, je na konci cyklu modifikován obsah registru Adr\_BF a vyvoláno přerušení.

Přesný popis obsluhy vyrovnávacích zásobníků je uveden v následující kapitole.

#### 6. Zpracování povelů od PC

V průběhu celé smyčky mikropočítač průběžně (cca 8x v průběhu celé smyčky) testuje stav registru POVEL a vykonává jejich obsluhu.

# 8. Popis programové podpory

# 8.1. Úvod

Dále uvedený popis odráží stav firmware verze 1.08; nově implemetované funkce pak budou dokumentovány podle jejich rozsahu v dodatcích uživatelské příručky v souborech na doprovodné disketě nebo v samostatné příručce.

Další popis této kapitoly je vztažen k pracovnímu režimu desky RUN po provedené inicializaci a dokončeném předešlém povelu.

# 8.2. Čtení obsahu základního datového bloku

Data základního datového bloku (tzn. rozsah adres 0..63) jsou určena pro případ, kdy aplikace vyžaduje nízkou, případně proměnnou četnost dat.

Přestože možností programové obsluhy je více, lze doporučit režim, ve kterém PC karta trvale aktualizuje data v RAM a pouze při požadavku aplikačního programu je aktualizace pozastavena. Pro takovou obsluhu byl firmware optimalizován a časová odezva na povel "zákaz zápisu" je výrazně kratší než na povel "povolení zápisu".

Dále uvedený postup znázorňuje posloupnost kroků potřebných ke korektnímu načtení dat:

- vyčkat na provedení předešlého povelu, tzn. na nulový obsahu registru Povel (pro případ, že se program obrací na kartu před provedením předešlého povelu)

- do registru Povel zapsat hodnotu 1 (= zákaz zápisu dat do DPRAM)

- vyčkat na provedení povelu, tzn. na vynulování obsahu registru Povel (zpracování tohoto povelu trvá maximálně 250µs)

- načíst požadovaná data z DPRAM (AINx, CNTx, ...)

- do registru Povel zapsat hodnotu 2 (= povolení přenosu dat do DPRAM) (zpracování povelu trvá maximálně 4ms a zahrnuje jednu aktualizaci dat)

# 8.3. Řízení analogových výstupů

Analogové výstupy jsou ovládány výhradně svými datovými registry a data v nich uložená jsou mikropočítačem průběžně zpracovávána. Každá změna se tedy na odpovídajícím výstupu projeví nejpozději po uplynutí doby jednoho cyklu (=2ms).

Aby byl přechodný stav při řízení analogových výstupů minimalizován, je potřeba, aby programování obou byte registru následovalo bezprostředně za sebou. Pořadí není významné.

# 8.4. Řízení čítačů

Pro řízení činnosti čítačů jsou vyhrazeny řídicí registry Ctrl\_CNT0 ÷ Ctrl\_CNT3. Registry mají významné dva nejnižšší bity a jejich význam je následující:

bit D0 slouží k povolení čítání

zápisem hodnoty "1" je čítání je povoleno, 0 ~ čítání je blokováno)

bit D1 slouží k nulování čítače

- zápisem logické hodnoty "1" je předán příkaz k vynulování čítače

- po vynulování se bit automaticky vrací do logické hodnoty "0"

🙇 – Čtení obsahu čítačů bylo popsáno v odstavci Čtení obsahu základního datového bloku.

### 8.5. Programová obsluha vyrovnávacích zásobníků

Přenos dat s využitím vyrovnávacích zásobníků je určen pro aplikace s vyššími požadavky na vzorkovací frekvenci.

PC karta střídavě zaplňuje dvojici zásobníků definovanou vzorkovací frekvencí postupem popsaným v kapitole "Popis činnosti firmware".

Aplikační program s využitím přerušení nebo softwarovým vyhodnocováním obsahu registru Adr\_BF detekuje probíhající zápisy dat a z "volného" bloku přenáší data ke zpracování.

K programové podpoře tohoto režimu jsou vyhrazeny následující registry:

| Adr_BF  | počáteční adresa zásobníku, který je zpracováván mikropočítačem 80 <sub>H</sub> mikropočítač zapisuje do zásobníku BLK_0                                                                                                        |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | CO <sub>H</sub> mikropočítač zapisuje do zásobníku BLK_1                                                                                                                                                                        |

| Ctrl_BF | počet vynechaných cyklů při přenosu dat do zásobníků  0 do zásobníků jsou přenášena data ze všech cyklů  1 do zásobníků jsou přenášena data z každého druhého cyklu  2 do zásobníků jsou přenášena data z každého třetího cyklu |

|         | 255 do zásobníků jsou přenášena data z každého 256. cyklu                                                                                                                                                                       |

Obsah registru Ctrl BF je po startu firmware nastaven na 49, tzn. vzorkovací periodu 100ms.

#### Postup programové obsluhy:

Po úvodní inicializaci registrů CW\_Reg a Ctrl\_BF mikropočítač střídavě zapisuje do BLK\_0 a BLK\_1. Stav registru Adr\_BF je modifikován ihned po dokončení zápisu do bloku, tzn. mikropočítač nastaví hodnotu C0<sub>H</sub> ihned po dokončení zápisu do bloku BLK\_0, resp. hodnotu 80<sub>H</sub> ihned po dokončení zápisu do bloku BLK\_1. V případě programové detekce zaplnění vyrovnávacích zásobníků program cyklicky vyhodnocuje stav registru Adr\_BF a při každé změně načte požadovaná data. V případě obsluhy s využitím přerušení je detekce stavu registru Adr\_BF a přenos dat realizován v rámci obslužné rutiny; přerušení je automaticky vyvoláno vždy při změně stavu registru Adr\_BF (předpokladem je korektní volba IRQ kanálu - viz popis CWReg).

#### Důležité upozornění.

Přenos dat ze zásobníku musí být proveden dříve než dojde k nové změně registru Adr BF.

Pro případ možného restartu firmware obvodem watchdog lze doporučit občasné testování obsahu CNT\_ON (obsahuje provozní čas od posledního startu firmware).

|         | SW1     |         |         |         |         |         |                  |  |

|---------|---------|---------|---------|---------|---------|---------|------------------|--|

| SW1 - 2 | SW1 - 3 | SW1 - 4 | SW1 - 5 | SW1 - 6 | SW1 - 7 | SW1 - 8 | (BASE)           |  |

| ON      | 200 <sub>H</sub> |  |

| ON      | ON      | ON      | ON      | ON      | ON      | OFF     | 204 <sub>H</sub> |  |

|         |         |         |         |         |         |         |                  |  |

| OFF     | ON      | ON      | ON      | ON      | ON      | ON      | 300 <sub>H</sub> |  |

| OFF     | ON      | ON      | ON      | ON      | ON      | OFF     | 304 <sub>н</sub> |  |

|         |         |         |         |         |         |         |                  |  |

| OFF     | OFF     | OFF     | OFF     | OFF     | OFF     | ON      | 3F8 <sub>H</sub> |  |

| OFF     | 3FС <sub>н</sub> |  |

Tab.1. SW1 - volba bázové adresy karty.

囱

$Adresa\ 300_{H}\ vyznačen\'a\ v\ tabulce\ je\ nastavena\ od\ v\'yrobce.$  Segment SW1-1 je rezervován.

| Počáteční adresa | Koncová adresa   | l/O zařízení                       |

|------------------|------------------|------------------------------------|

| 200 <sub>H</sub> | 207 <sub>H</sub> | adapter pro hry                    |

| 278 <sub>H</sub> | 27F <sub>H</sub> | 2. tiskárna                        |

| 2F8 <sub>H</sub> | 2FF <sub>H</sub> | 2. adapter asynchronní komunikace  |

| 300 <sub>H</sub> | 31F <sub>H</sub> | prototypová deska                  |

| 360 <sub>H</sub> | 36F <sub>H</sub> | rezerva                            |

| 378 <sub>H</sub> | 37F <sub>H</sub> | 1. tiskárna                        |

| 380 <sub>H</sub> | 38F <sub>H</sub> | synchronní komunikace SDLC         |

| 3A0 <sub>H</sub> | 3AF <sub>H</sub> | synchronní komunikace BSC          |

| 3B0 <sub>H</sub> | 3BF <sub>H</sub> | monochromatický display + tiskárna |

| 3C0 <sub>H</sub> | 3CF <sub>H</sub> | rezerva                            |

| 3D0 <sub>H</sub> | 3DF <sub>H</sub> | barevný display                    |

| 3F0 <sub>H</sub> | 3F7 <sub>H</sub> | řadič disket                       |

| 3F8 <sub>H</sub> | 3FF <sub>H</sub> | 1. adapter asynchronní komunikace  |

Tab.2. Seznam standardních adres I/O zařízení.

| funkce  | PIN       | PIN | funkce    |

|---------|-----------|-----|-----------|

| A GND   | C13       | 005 | A / A / A |

| AOUT0   | C12       | C25 | AIN0      |

| AOUT1   | C11       | C24 | AIN1      |

| AOUT2   | C10       | C23 | AIN2      |

| AOUT3   | C9        | C22 | AIN3      |

|         |           | C21 | AIN4      |

| AOUT4   | C8        | C20 | AIN5      |

| AOUT5   | <i>C7</i> | C19 | AIN6      |

| AOUT6   | C6        | C18 | AIN7      |

| AOUT7   | C5        |     | AllV7     |

|         | C4        | C17 |           |

|         | СЗ        | C16 |           |

| PWR GND | C2        | C15 | PWR GND   |

|         |           | C14 | +12V      |

| +5V     | C1        |     |           |

Tab.3. Zapojení vývodů konektoru Cannon 25.

Výstupy +5V a +12V lze zatížit proudem 2x 500mA.

| funkce   | PIN | PIN      | funkce  |

|----------|-----|----------|---------|

| GND      | C5  | <u> </u> | CNT INO |

| CNT_IN1  | C4  | C9       | CNT_IN0 |

| CNT_IN3  | C3  | C8       | CNT_IN2 |

| PROG OUT | C2  | C7       |         |

| +5V      | C1  | C6       |         |

Tab.4. Zapojení vývodů konektoru Cannon 9.

Výstup +5V lze zatížit proudem 500mA. Signál PROG OUT je určen jako rezerva pro budoucí využití.

| funkce       | PIN | PIN | funkce       |

|--------------|-----|-----|--------------|

| DIN0 / DOUT0 | D1  | D2  | DIN1 / DOUT1 |

| DIN2 / DOUT2 | D3  | D4  | DIN3 / DOUT3 |

| DIN4 / DOUT4 | D5  | D6  | DIN5 / DOUT5 |

| DIN6 / DOUT6 | D7  | D8  | DIN7 / DOUT7 |

| GND          | D9  | D10 | +5V          |

Tab.5. Zapojení vývodů konektorů DIL10.

| funkce          | PIN       | PIN       | funkce       |

|-----------------|-----------|-----------|--------------|

| GND             | C5        |           |              |

| DING / DOUTS    | 0.1       | C9        | DIN7 / DOUT7 |

| DIN6 / DOUT6    | C4        | C8        | DIN5 / DOUT5 |

| DIN4 / DOUT4    | <i>C3</i> |           |              |

| DIN2 / DOUT2    | C2        | <i>C7</i> | DIN3 / DOUT3 |

| DIN2 / DOUT2    | 02        | C6        | DIN1 / DOUT1 |

| DIN0 / DOUT0 C1 |           | 5, 5.6611 |              |

| <u> </u>        |           |           |              |

Tab.6. Zapojení vývodů konektorů Cannon 9 (DIG-14).

| I/O adresa | registr   |          |  |

|------------|-----------|----------|--|

|            | WR        | RD       |  |

| BASE+0     | RAMReg    |          |  |

| BASE+1     | ADRReg    |          |  |

| BASE+2     | DigOutReg | DigInReg |  |

| BASE+3     | CWReg     | STSReg   |  |

Tab.7. Vnitřní struktura adresového prostoru karty.

| adresa    | registr   | význam                                                                                                                                                                                                                                                                                     |

|-----------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 ÷ 1     | AIN0      | 12-bitová hodnota analogového vstupu AINO (0÷4095)                                                                                                                                                                                                                                         |

|           |           |                                                                                                                                                                                                                                                                                            |

| 14 ÷ 15   | AIN7      | 12-bitová hodnota analogového vstupu AIN7 (0÷4095)                                                                                                                                                                                                                                         |

| 16 ÷ 19   | CNT0      | 32-bitová hodnota čítače CNT0                                                                                                                                                                                                                                                              |

|           |           |                                                                                                                                                                                                                                                                                            |

| 28 ÷ 31   | CNT3      | 32-bitová hodnota čítače CNT3                                                                                                                                                                                                                                                              |

| 32 ÷ 35   | CNT_ON    | 32-bitová hodnota čítače provozního času<br>(čas v ms od startu firmware)                                                                                                                                                                                                                  |

| 36        | CNT_IN    | aktuální stav vstupů čítačů CNT_IN0 ÷ CNT_IN3<br>(každý vstup reprezentován jedním bitem registru)                                                                                                                                                                                         |

| 37 ÷ 63   | NC        | nevyužito - rezerva                                                                                                                                                                                                                                                                        |

| 64 ÷ 65   | AOUT0     | 12-bitová hodnota analogového výstupu AOUT0 (0÷4095)                                                                                                                                                                                                                                       |

|           |           |                                                                                                                                                                                                                                                                                            |

| 78 ÷ 79   | AOUT7     | 12-bitová hodnota analogového výstupu AOUT7 (0÷4095)                                                                                                                                                                                                                                       |

| 80 ÷ 95   | NC        | nevyužito - rezerva                                                                                                                                                                                                                                                                        |

| 96 ÷ 111  | TYP       | 16-znakový řetězec s názvem karty a verzí firmware<br>(např. PCA-1288 1.08)                                                                                                                                                                                                                |

| 112       | Ctrl_CNT0 | řídicí registr čítače CNT0<br>bit D0: H ~ čítač pracuje, L ~ čítač je blokován<br>bit D1: H ~ nulování čítače (bit se automaticky vrací do L)                                                                                                                                              |

|           |           | ****                                                                                                                                                                                                                                                                                       |

| 115       | Ctrl_CNT3 | řídicí registr čítače CNT3                                                                                                                                                                                                                                                                 |

| 116       | Ctrl_BF   | řídicí registr AIN - četnost přenosu dat do zásobníků<br>0 ~ zásobník zaplňován v každém cyklu<br>1 ~ zásobník zaplňován v každém druhém cyklu (jeden vypuštěn)<br>2 ~ zásobník zaplňován v každém třetím cyklu (dva vypuštěny)<br>N ~ zásobník zaplňován v každém N+1 cyklu (N vypuštěno) |

| 117       | Adr_BF    | ukazatel aktuálně zpracovávaného bloku zásobníku<br>(nabývá hodnoty 128 nebo 192, tzn. počáteční adresy bloku)                                                                                                                                                                             |

| 118 ÷ 125 | NC        | nevyužito - rezerva                                                                                                                                                                                                                                                                        |

| 126       | Status    | registr stavových příznaků<br>bit D0: H ~ základní datový blok průběžně aktualizován                                                                                                                                                                                                       |

| 127       | Povel     | řídicí registr registr<br>0 ~ klidový stav (= povel zpracován)<br>1 ~ zákaz zápisu dat do základního datového bloku (0÷63)<br>2 ~ povolení zápisu dat do základního datového bloku (0÷63)                                                                                                  |

| 128 ÷ 191 | BLK_0     | 1. blok vyrovnávacího zásobníku<br>(registrová struktura shodná se základním datovým blokem 0÷63)                                                                                                                                                                                          |

| 192 ÷ 255 | BLK_1     | 2. blok vyrovnávacího zásobníku<br>(registrová struktura shodná se základním datovým blokem 0÷63)                                                                                                                                                                                          |

#### Tab.7. Struktura adresového prostoru dvoubránové paměti.

Dvoubytové a čtyřbytové parametry jsou do RAM ukládány v pořadí nejnižším byte počínaje a s nevyužitými nejvyššími bity. Tzn. na adrese 0 jsou uloženy bity AIN0(7..0), na adrese 1 pak bity AIN0(15..8) a vzhledem k 12-bitovému rozlišení jsou nejvyšší čtyři bity trvale nulové).

Obr.1. Vnitřní struktura karet řady PCA-1288.

Obr.2. Rozmístění důležitých prvků na kartě PCA-1288.

Obr.3. Rozmístění vývodů na konektoru Cannon 25.

Obr.4. Rozmístění vývodů na konektoru Cannon 9.

Obr.5. Rozmístění vývodů na konektoru DIL 10.

Obr.6. Propojovací kabel s PC štítkem DIG-14, rozmístění portů na konektorech.

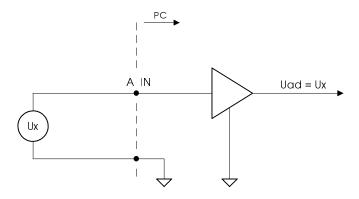

# Obr.7. Připojení analogového vstupu karty.

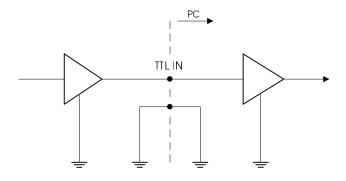

### Obr.8. Připojení digitálních a frekvenčních vstupů karty.

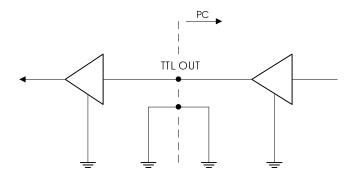

### Obr.9. Připojení digitálních a frekvenčních výstupů karty.